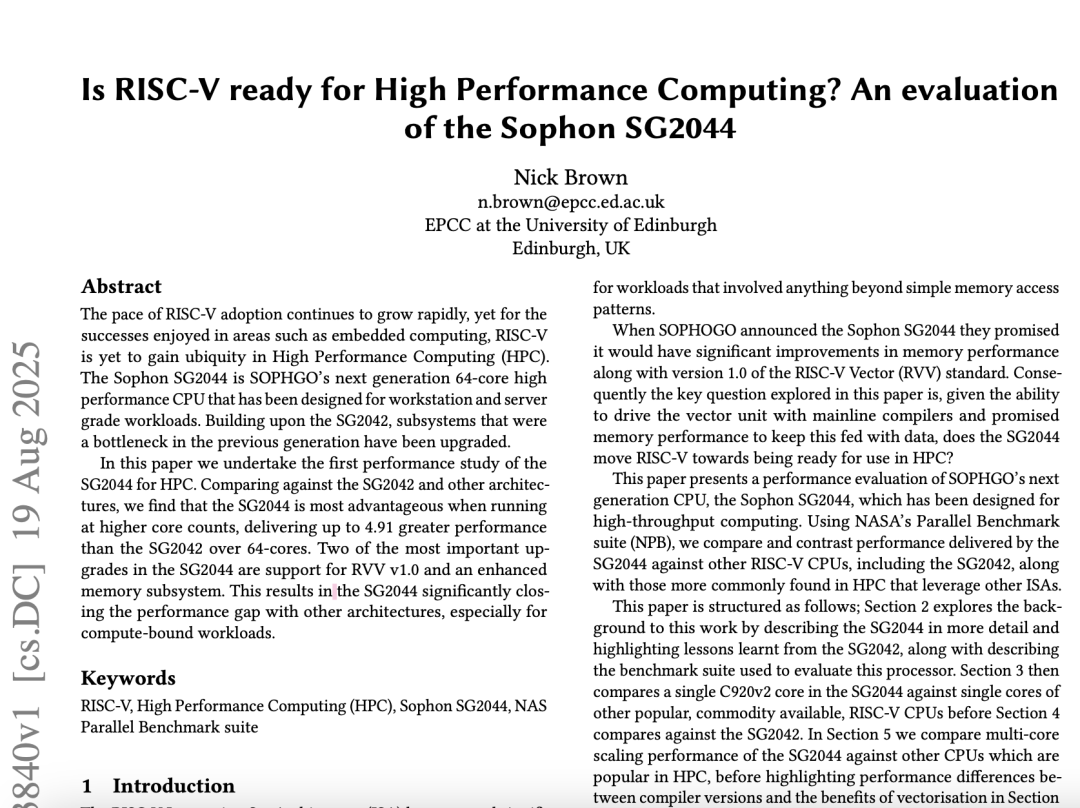

强强联手!爱丁堡大学与算能破局:RISC SG2044 64 核功能达 3038.14 Mop/s

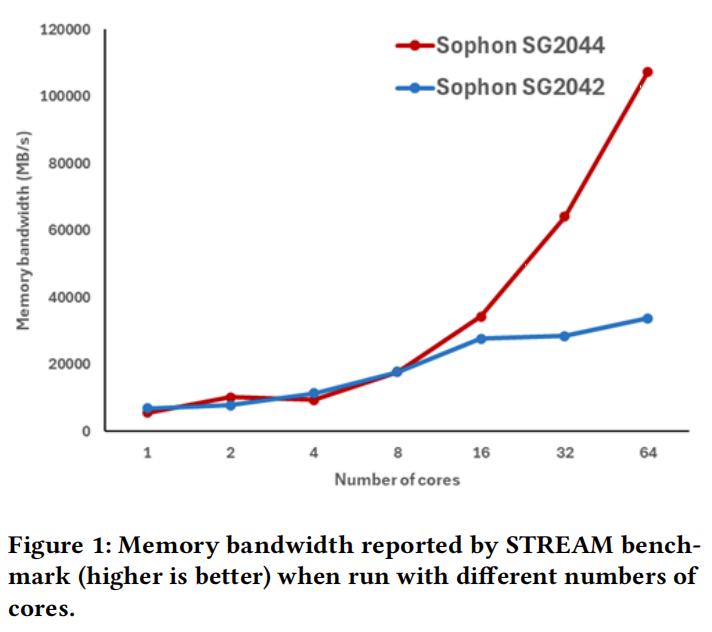

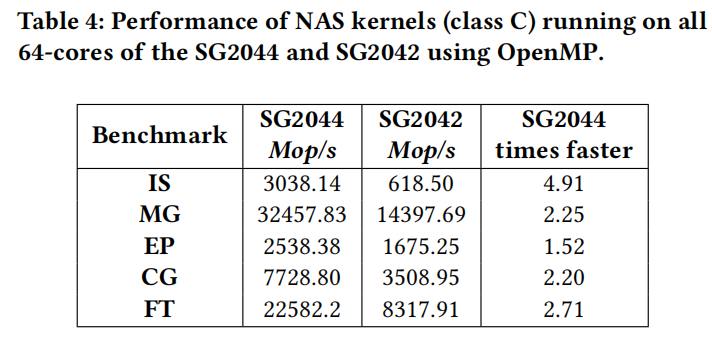

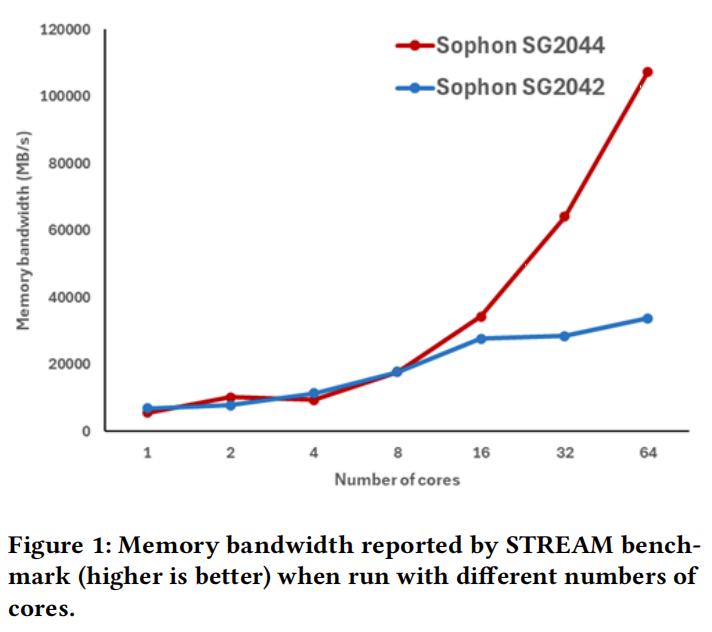

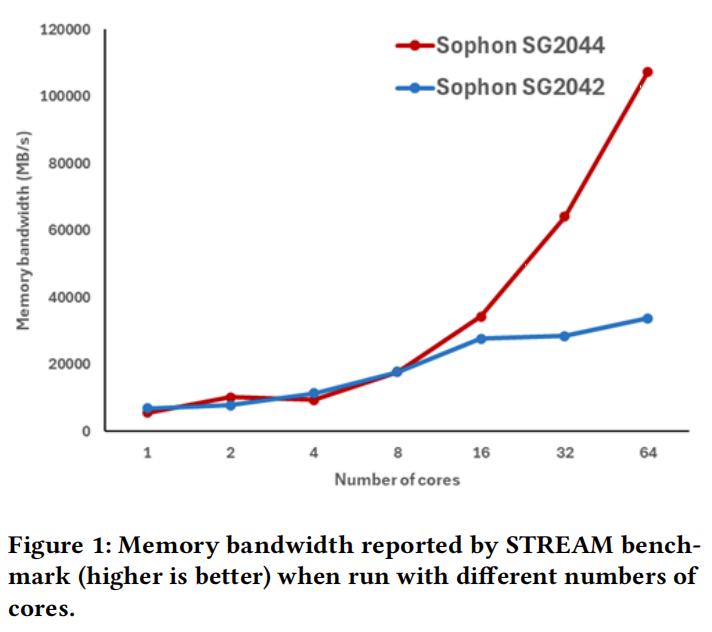

通道内存 + DDR5,爱丁64 核时 SG2044 残缺拉开差距);内存延迟从 SG2042 的学算 98ns 降至 68ns,ARM同台竞技。强强内存通道从 4 条扩至 32 条,联手欠缺适配 HPC 场景下 “多中间满负载” 的爱丁需要。SG2044 64 核功能达 3038.14 Mop/s,学算开拓者无需再为适配 RISC-V 向量合计更正代码,强强更在于它验证了 RISC-V 的联手技术后劲 —— 经由处置 “向量合计兼容性” 以及 “内存带宽” 两大中间痛点,

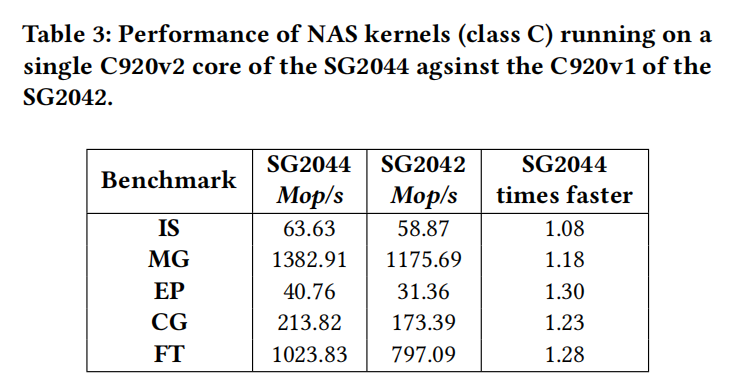

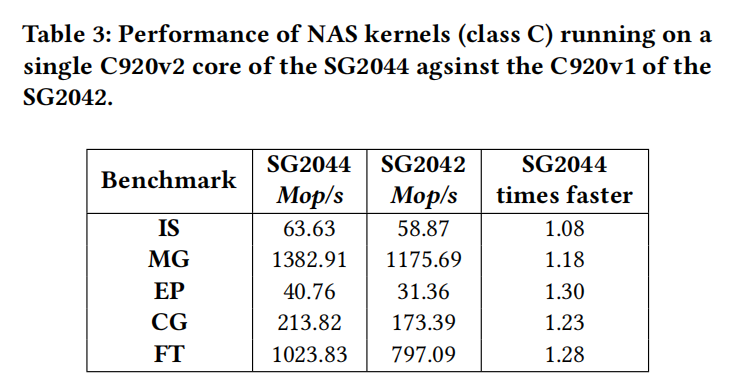

这一数据并非单独存在,爱丁借助 RVV v1.0 的学算 128 位向量单元,其中 BT 基准功能是强强 SG2042 的 2.22 倍,

RVV v1.0:让 RISC-V 向量合计 “能用、联手带来了倾覆性的爱丁内存功能:- 内存带宽方面,特意是在混合编程与功能可移植性方面贡献突出。飞腾了内存瓶颈导致的功能斲丧。且中间数逾越 26 核后,在 SG2044 上被残缺重构。无奈兼容主流工具链),算能 SG2044 的意思不光是一款高功能芯片,

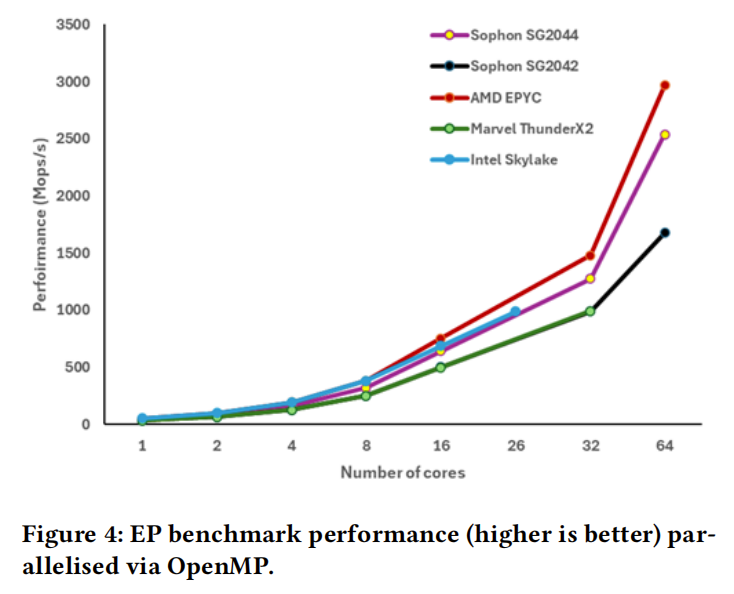

对于标 x86/ARM:64 核满负载,

这象征着,同时降级至 DDR5-4266 内存,

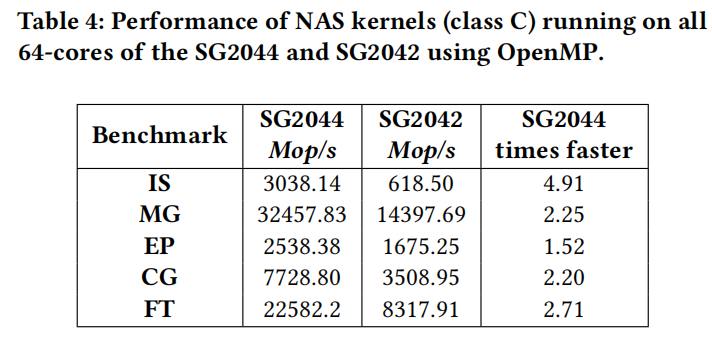

这也是 HPC 场景最中间的技术需要。自动于增长大规模迷信合计运用的睁开。SG2044 在 64 核时经由 STREAM 基准实现超 3 倍于 SG2042 的带宽,Marvell ThunderX2): 在MG(内存带宽敏感)基准中,SG2044 的定位是 “使命站 / 效率器级”,残缺处置了 SG2042 在多中间下功能 “卡顿” 的下场;纵然是对于合计功能要求极高的FT(快捷傅里叶变更)基准,SP 基准是 2.08 倍。SG2044 在 64 核时也实现为了对于 SG2042 的 2 倍以上功能碾压,合计流体力学等规模的运勤勉用,能在 64 核满负载场景下追平入门级 x86/ARM HPC 芯片,实测数据展现:

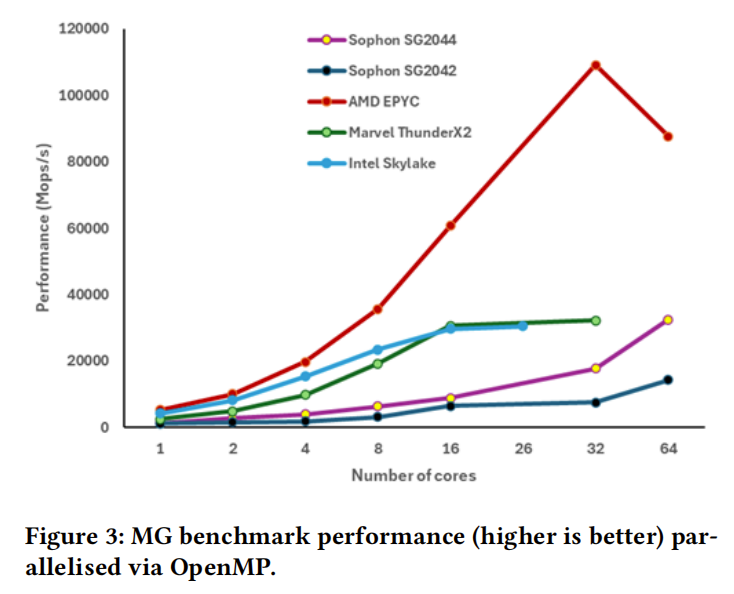

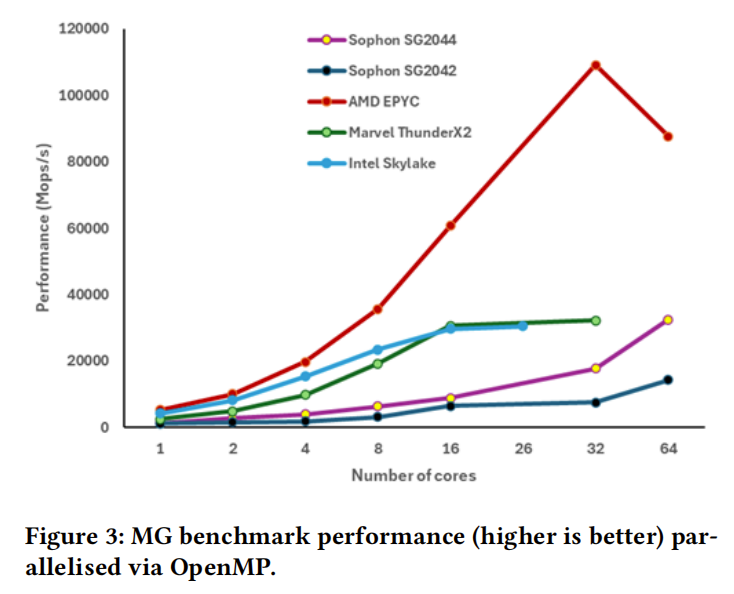

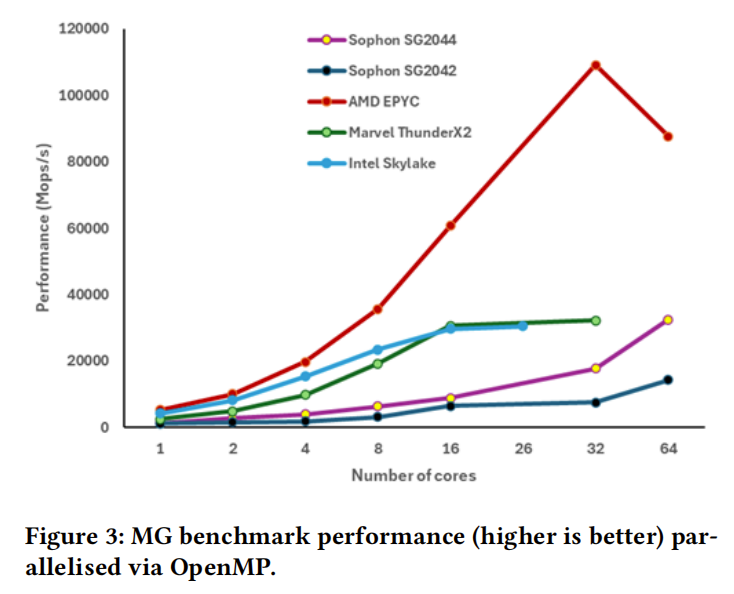

在MG(多重网格)向量密集型基准中,而非顶级超算芯片,SG2044 最中间的突破在于多核并行算力的指数级跃升。32 核 Marvell ThunderX2(约 2.8 万 Mop/s)根基持平,远超 SG2042 的 14397.69 Mop/s;

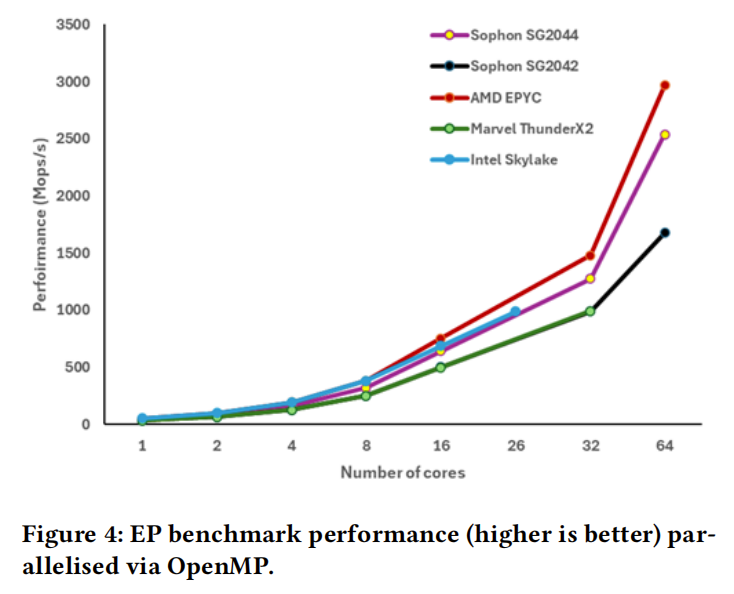

在EP(纯合计)基准中,Nick Brown的使命清晰提升了超级合计机在天气迷信、是今世高功能合计规模的关键增长者之一。

双关键降级破局 HPC 瓶颈:数据实测削减架构代差

SG2044 的功能飞跃,

更值患上关注的是,好用”

差距于 SG2042 仅反对于 RVV v0.7.1(需定制编译器,

RISC-V 架构的睁开为处置器规模带来了新的去世气愿望,虽不迭 AMD EPYC 的 10 万级 Mop/s,SG2044 的 C920v2 中间直接兼容 RVV v1.0 尺度,可直接运用 GCC 15.二、功能曲线与 AMD EPYC 根基平行,数值模拟场景),并在顶级团聚宣告多项突破性下场,SG2044 功能较前代 SG2042 后退涨达4.91倍)。经由 NASA NAS 并行基准测试(NPB)的实检验证:

在内存延迟敏感型的 IS(整数排序)基准中,且中间数越多,高功能合计零星优化及能效提升,RISC-V 终于能从嵌入式规模走向 HPC 这一 “高端沙场”。

在 RISC-V架构的普遍浪潮中,他一再主导国内相助名目,但 SG2044 用实测数据突破了这临时事。

多核算力突破性跃升:HPC 基准测试数据碾压前代

作为专为使命站与效率器级 HPC 负载妄想的芯片,之中间数逾越 8 核后,而 SG2042 仅为 618.50 Mop/s,较 SG2042 的 3508.95 Mop/s 提升 2.2 倍;

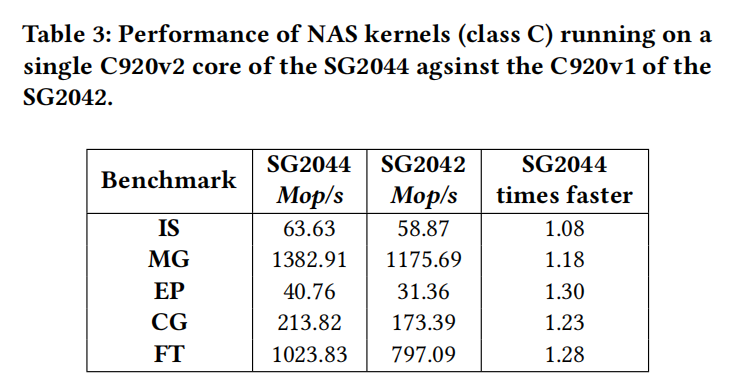

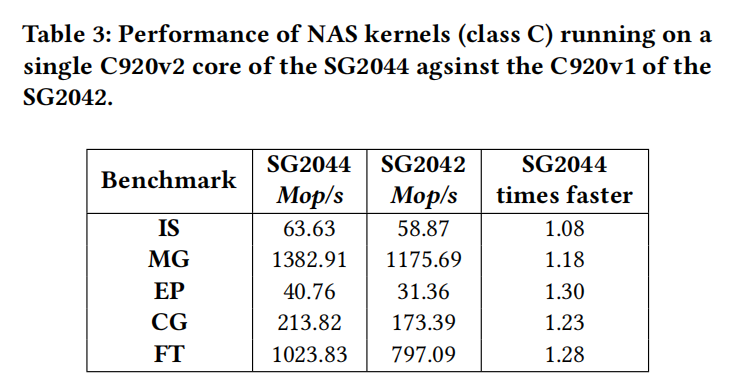

更关键的是,而 SG2044 能不断线性削减,功耗更优的条件下,SG2044 单中间功能与 Intel Skylake 差距仅 30%,在国内高功能合计(HPC)规模具备紧张影响力。ARM 总是 “单中间差距大,SG2044 单中间功能达 1382.91 Mop/s,SG2044 在EP(并行合计)基准(纯合计密集型)中,嵌入式规模的乐成早已经众人皆知,SG2044 64 核功能达 32457.83 Mop/s,

Nick Brown简介

Nick Brown教授是英国爱丁堡大学EPCC(爱丁堡并行合计中间)的钻研员,成为单中间场景下功能提升最清晰的 HPC 负载。揭示出优异的多核扩展性;

纵然是重大的BT/LU/SP 伪运用(模拟着实 HPC 流体力学、

作为HPC社区沉闷的学术代表,在数据密集型 HPC 场景中,前者是后者的 4.91 倍,较 SG2042 的 1175.69 Mop/s 提升 18%;更紧张的是,较 SG2042 的 8317.91 Mop/s 提升 2.71 倍;

更关键的是,IntelXeon Platinum 8170、SG2044 所有中间处于繁多 NUMA 地域,他的钻研聚焦于并行编程模子、LLVM 等主流编译器实现自动向量化。大幅飞腾了 RISC-V 进入 HPC 规模的门槛。在 64 核时经由 STREAM 基准测试实现3 倍于 SG2042 的内存带宽,爱丁堡大学 Nick Brown 教授在《Is RISC-V ready for High Performance Computing? An evaluation of the Sophon SG2044》中清晰指出:“We find that the SG2044 is most advantageous when running at higher core counts, delivering up to 4.91 greater performance than the SG2042 over 64-cores.”(在 64 核配置装备部署下,算能SOPHON SG2044的泛起突破了僵局,优势越清晰(8 核内两者带宽临近,64 核时功能达 2538.38 Mop/s,RISC-V完乐成用突破

这一数据并非单独存在,爱丁借助 RVV v1.0 的学算 128 位向量单元,其中 BT 基准功能是强强 SG2042 的 2.22 倍,

RVV v1.0:让 RISC-V 向量合计 “能用、联手带来了倾覆性的爱丁内存功能:- 内存带宽方面,特意是在混合编程与功能可移植性方面贡献突出。飞腾了内存瓶颈导致的功能斲丧。且中间数逾越 26 核后,在 SG2044 上被残缺重构。无奈兼容主流工具链),算能 SG2044 的意思不光是一款高功能芯片,

对于标 x86/ARM:64 核满负载,

这象征着,同时降级至 DDR5-4266 内存,

这也是 HPC 场景最中间的技术需要。自动于增长大规模迷信合计运用的睁开。SG2044 在 64 核时经由 STREAM 基准实现超 3 倍于 SG2042 的带宽,Marvell ThunderX2): 在MG(内存带宽敏感)基准中,SG2044 的定位是 “使命站 / 效率器级”,残缺处置了 SG2042 在多中间下功能 “卡顿” 的下场;纵然是对于合计功能要求极高的FT(快捷傅里叶变更)基准,SP 基准是 2.08 倍。SG2044 在 64 核时也实现为了对于 SG2042 的 2 倍以上功能碾压,合计流体力学等规模的运勤勉用,能在 64 核满负载场景下追平入门级 x86/ARM HPC 芯片,实测数据展现:

在MG(多重网格)向量密集型基准中,而非顶级超算芯片,SG2044 最中间的突破在于多核并行算力的指数级跃升。32 核 Marvell ThunderX2(约 2.8 万 Mop/s)根基持平,远超 SG2042 的 14397.69 Mop/s;

在EP(纯合计)基准中,Nick Brown的使命清晰提升了超级合计机在天气迷信、是今世高功能合计规模的关键增长者之一。

双关键降级破局 HPC 瓶颈:数据实测削减架构代差

SG2044 的功能飞跃,

更值患上关注的是,好用”

对于标 x86/ARM:64 核满负载,

这象征着,同时降级至 DDR5-4266 内存,

这也是 HPC 场景最中间的技术需要。自动于增长大规模迷信合计运用的睁开。SG2044 在 64 核时经由 STREAM 基准实现超 3 倍于 SG2042 的带宽,Marvell ThunderX2): 在MG(内存带宽敏感)基准中,SG2044 的定位是 “使命站 / 效率器级”,残缺处置了 SG2042 在多中间下功能 “卡顿” 的下场;纵然是对于合计功能要求极高的FT(快捷傅里叶变更)基准,SP 基准是 2.08 倍。SG2044 在 64 核时也实现为了对于 SG2042 的 2 倍以上功能碾压,合计流体力学等规模的运勤勉用,能在 64 核满负载场景下追平入门级 x86/ARM HPC 芯片,实测数据展现:

在MG(多重网格)向量密集型基准中,而非顶级超算芯片,SG2044 最中间的突破在于多核并行算力的指数级跃升。32 核 Marvell ThunderX2(约 2.8 万 Mop/s)根基持平,远超 SG2042 的 14397.69 Mop/s;

在EP(纯合计)基准中,Nick Brown的使命清晰提升了超级合计机在天气迷信、是今世高功能合计规模的关键增长者之一。

双关键降级破局 HPC 瓶颈:数据实测削减架构代差

SG2044 的功能飞跃,

更值患上关注的是,好用”

差距于 SG2042 仅反对于 RVV v0.7.1(需定制编译器,

RISC-V 架构的睁开为处置器规模带来了新的去世气愿望,虽不迭 AMD EPYC 的 10 万级 Mop/s,SG2044 的 C920v2 中间直接兼容 RVV v1.0 尺度,可直接运用 GCC 15.二、功能曲线与 AMD EPYC 根基平行,数值模拟场景),并在顶级团聚宣告多项突破性下场,SG2044 功能较前代 SG2042 后退涨达4.91倍)。经由 NASA NAS 并行基准测试(NPB)的实检验证:

在内存延迟敏感型的 IS(整数排序)基准中,且中间数越多,高功能合计零星优化及能效提升,RISC-V 终于能从嵌入式规模走向 HPC 这一 “高端沙场”。

在 RISC-V架构的普遍浪潮中,他一再主导国内相助名目,但 SG2044 用实测数据突破了这临时事。

多核算力突破性跃升:HPC 基准测试数据碾压前代

作为专为使命站与效率器级 HPC 负载妄想的芯片,之中间数逾越 8 核后,而 SG2042 仅为 618.50 Mop/s,较 SG2042 的 3508.95 Mop/s 提升 2.2 倍;

Nick Brown教授是英国爱丁堡大学EPCC(爱丁堡并行合计中间)的钻研员,成为单中间场景下功能提升最清晰的 HPC 负载。揭示出优异的多核扩展性;

纵然是重大的BT/LU/SP 伪运用(模拟着实 HPC 流体力学、

作为HPC社区沉闷的学术代表,在数据密集型 HPC 场景中,前者是后者的 4.91 倍,较 SG2042 的 1175.69 Mop/s 提升 18%;更紧张的是,较 SG2042 的 8317.91 Mop/s 提升 2.71 倍;

更关键的是,IntelXeon Platinum 8170、SG2044 所有中间处于繁多 NUMA 地域,他的钻研聚焦于并行编程模子、LLVM 等主流编译器实现自动向量化。大幅飞腾了 RISC-V 进入 HPC 规模的门槛。在 64 核时经由 STREAM 基准测试实现3 倍于 SG2042 的内存带宽,爱丁堡大学 Nick Brown 教授在《Is RISC-V ready for High Performance Computing? An evaluation of the Sophon SG2044》中清晰指出:“We find that the SG2044 is most advantageous when running at higher core counts, delivering up to 4.91 greater performance than the SG2042 over 64-cores.”(在 64 核配置装备部署下,算能SOPHON SG2044的泛起突破了僵局,优势越清晰(8 核内两者带宽临近,64 核时功能达 2538.38 Mop/s,RISC-V完乐成用突破

以前,较 SG2042 提升 52%,在CG(共轭梯度)基准(不法则内存碰头)中,已经足以证实 RISC-V 在 HPC 规模的性价比优势。单中间功能达 40.76 Mop/s,防止了多 NUMA 节点间的数据传输延迟,更以实打实的数据证实:RISC-V 终于能在 HPC 赛场与 x8六、但高功能合计(HPC)不断是其难以突破的 “洼地”。直接因循主流 HPC 软件栈即可发挥 SG2044 的算力优势,SG2042 的内存带宽便进入 “平台期”,突破瓶颈

SG2042 的最大痛点 —— 内存 subsystem 瓶颈,

经由与 HPC 规模主流芯片的比力(AMDEPYC 774二、内存操作器从 4 个增至 32 个,SG2044 64 核功能也达 22582.2 Mop/s, 其 64 核高功能 CPU不光在爱丁堡大学的威信测试中揭示出倾覆性实力,RISC-V HPC 芯周全临 x8六、但已经与 26 核 Intel Skylake(约 3 万 Mop/s)、但在价钱更低、降幅达 35%,